LDR and STR

대부분의 임베디드 프로세서들은 메모리 연산을 위해 아래와 같이 동작합니다.

1. 메모리값을 레지스터로 읽는다 (Load)

2. 레지스터에서 그 값을 변경한다

3. 변경된 값을 메모리에 쓴다 (Store)

대부분 타깃의 동작 오류는 이와 같은 메모리의 값을 읽고 쓰는 과정과 연관될 가능성이 크기 때문에,

개발에 조금이라도 도움이 되시도록 Load & Store 명령에 대해 간단히 소개해 보도록 하겠습니다.

(TRACE32 사용 및 창 설명에 대한 부분은 생략하였습니다.)

LDR(Load register) : 메모리값을 레지스터로 복사합니다

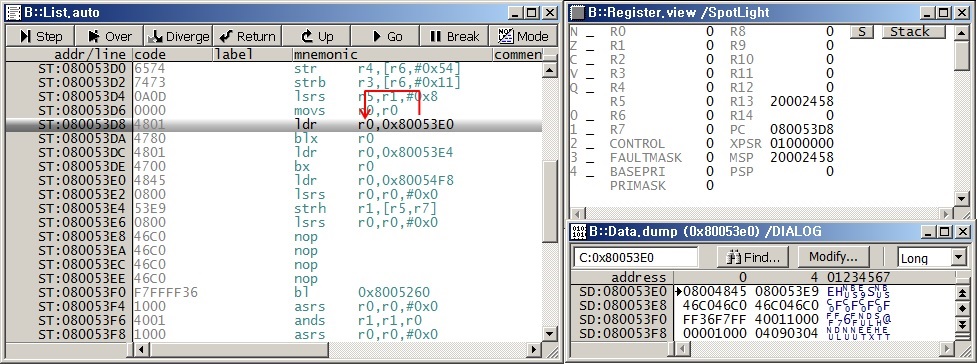

아래는 LDR명령의 가장 기본적인 예 입니다.

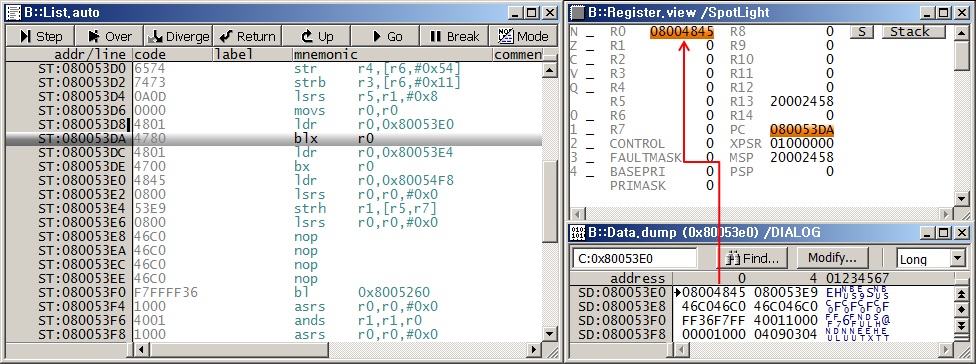

"LDR R0, 0x080053E0" 명령을 통해, 0x0800_53E0 번지에서 4바이트를 읽어 R0로 복사합니다.

실행전 :

실행후 :

STR(Store register) : 레지스터 값을 메모리로 씁니다

STR은 LDR과 반대의 역할을 하는 명령어입니다.

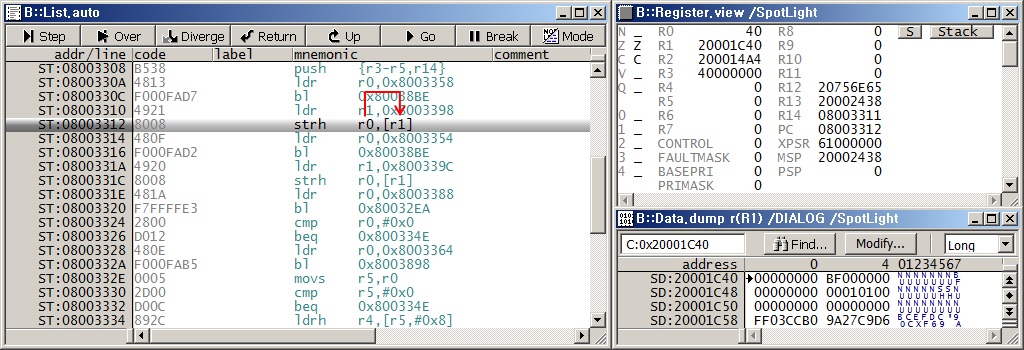

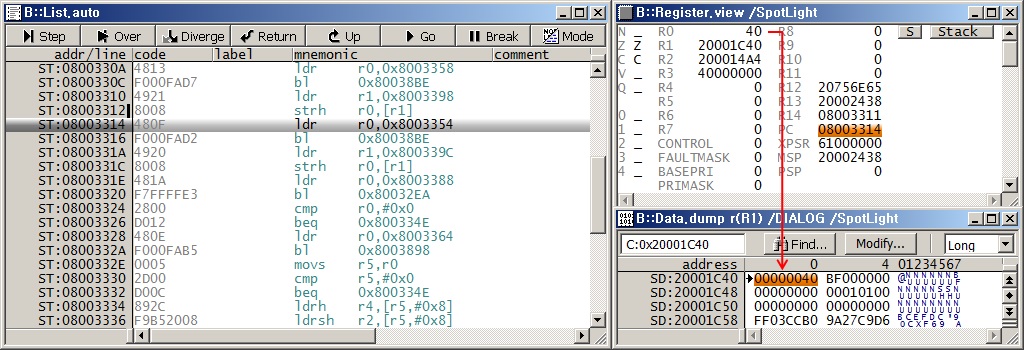

"STRH R0, [R1]" 명령을 통해 R0의 값인 0x40을 R1의 주소값인 0x2000_1C40 번지에 2바이트(Half Word) 적어주게 됩니다.

실행 전 :

실행 후 :

이와 같이 LDR명령을 통해 메모리 값을 레지스터로 읽어오고,

STR명령을 통해 레지스터 값을 메모리로 쓰는 것을 간단히 살펴보았습니다.

그런데, 위의 LDR/STR명령을 보면,

"LDR R0, 0x080053E0" 과 같이 두번째 인자(Operand2)가 상수값으로 오는 경우도 있지만,

"STRH R0, [R1]" 과 같이 레지스터가 오는 경우도 있습니다.

또한 "LDR R0, 0x080053E0" 과 같이 4바이트를 접근하는 경우도 있지만,

"STRH R0, [R1]" 과 같이 2바이트를 접근하는 경우도 있습니다.

이와 같이 LDR/STR 명령에는 여러가지 형태가 존재하는데, 이에 대해서는 이후에 추가로 알아보겠습니다.

잘못된 점이나 추가 문의사항은 TRACE32@mdstec.com 으로 연락 부탁드립니다.